# A Review on Junctionless Transistor - A Prospective sub-10nm Logic Device

Subhradip Das<sup>1</sup>, Sudakshina Kundu<sup>2</sup>

<sup>1</sup>Research Scholar, West Bengal University of Techology, BF-142, Salt Lake, Sector 1, Kolkata-700064, West Bengal, India

<sup>2</sup>West Bengal University of Techology, BF-142, Salt Lake, Sector 1, Kolkata-700064, West Bengal, India

*Abstract:* This paper reviews a new semiconductor device structure namely the Junctionless Transistor. This paper comprehensively presents the novel architecture of the Junctionless Transistor (JLT), which shows much promise in resolving the certain important issues related to the limitations of the conventional MOSFET and CMOS industry. The Junctionless Transistor has very low leakage currents, high onto-off current ratio, better sub threshold slope, improved transconductance and less degradation of the carrier mobility with gate voltage and temperature than the classical transistors. Such a structure can be also referred to as Junctionless Gated Resistor (JLGR). They have lesser number of much simpler fabrication steps and hence less production cost than other contemporary logic devices.

# 1. INTRODUCTION

The standard of human living has been greatly revolutionized by modern technologies. This is spearheaded by the advancement in semiconductor industry. The relevance of Semiconductor research is established by the recent Semiconductor Industry Associations' Reports [1] suggesting a worldwide turn over of an overwhelming \$305.6 Billion sales in the year 2013, clear 4.8% increase over the figures obtained the year before. Moores' Law [2] has guided the trends in technology in his prediction of the technology node that is eapected to half in every eigheen months. This eapects the packing density of the integrated circuits to be doubled in one and a half years. But owing to voracious geometrical scaling [3] the semiconductor device dimensions are nearing the physical limits [4,5] such that they can not be further scaled down without adversely affecting their performance. Thus the progress of the semiconductor inductry is on the verge of stagnation owing to the limitations that have been ushered in from various technological bottle necks. Efforts are now being made to get around the problem and reach the goals set up by the industry through the International Technology Roadmap for Semiconductors [6]. Such efforts have seen various research groups exploring novel device architectures, starting from the Strained Silicon Technologies [7] spanning the Silicon-on-Insulator (SOI) structures [8], the multi-GATE

architectures like the Fin-FETs [9-13] and other advanced Gate Engineered Transistors of late [14,15].

The main issues which stand in the way of success of the semiconductor devices in the deep sub-micron regime, (order of 10nm and below), are the sharp gradient in doping profiles, thermal budget issues for processing, various short channel effects like drain induced barrier lowering, punch through,etc. and finally the sub-threshold characteristics of such small dimensional devices. As predicted by ITRS 2012 reports, the geometrical gate length is stipulated to reach 9nm at around 2016. At such a small gate length the quantum mechanical effects like carrier quantisations become predominant. The source-substrate and drain substrate junction formation in small scale devices become very difficult as it requires sharp doping density gradient which causes thermal budgeting issues. The performance of such small scale devices deteriorate due to the various detrimental short channel effects [16]:

- drain-induced barrier lowering

- punch through

- surface scattering

- velocity saturation

- impact ionization

- hot electron effect

The narrow width effects also become predominantly large, bringing device performance metrices below tolerance limits. With the complexity of the device architectures, process variations and corresponding complexities increase manifold. Therefore the fabrication of such novel device structures involves costly equipments leading to rise in batch fabrication and production cost per chip. Hence simpler and novel device structures may prove to be potent enough to eliminate all the above drawbacks and perform well in the sub 10nm regime.

## 2. PHYSIC OF CURRENT CONDUCTION IN JUNCTIONLESS TRANSISTOR

It has been reported by J P Colinge et.al [17,18] the physics of the Junctionless Transistor (JLT) is very different from that of the MOSFET. Current conduction is a bulk phenomena in JLT. The normally on-channel conducts during the on-state when bias is applied across source and drain. The gate voltage induces depletion region in the channel to turn off the current. The channel depletion constricts the cross section of the channel and reduces the current flow. Finally the channel is pinched off. Since current conduction in JLT is a bulk phenomena, the channel needs to be made much thin for the gate voltage to be able to turn off the transistor. Also the channel region has to be highly doped in order to turn the channel on fast. The conduction phenomena in JLT is similar to that of the Field Effect Transistor.

# 3. REVIEW WORK

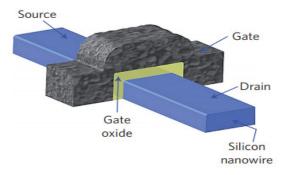

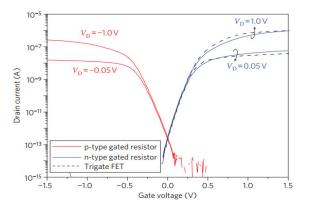

Figure 2: Current Voltage Charecteristics [17]

J P Colinge et.al in a paper entitled, "Nanowire transistors without junctions" [17] have established a novel MOSstructure, namely the Junctionless Transistor, that addresses all the above limitations as the physical channel length scales down to the order of 10nm. This device has been patented by the group [18]. This structure can be also referred to as Junctionless Gated Resistor. It has simpler and less number of fabrication steps than the conventional MOSFET. Hence the fabrication cost is less.

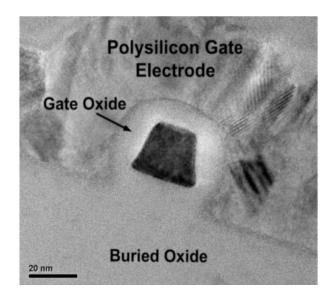

Figure 3: TEM cross section of a junctionless nanowire transistor[19].

Dr. A Kranti, J P Colinge and their research group have detailed the design guidelines of such a structure [19]. The Analog behaviour of Junctionless Transistor at temperatures ranging form 100K to 473K is presented by Dr. A Kranti, Prof. J P Colinge and their group [20]. In the paper entitled Multiple-Gate Transistors "Junctionless for Analog Applications" [21] the authors have pointed out that the device shows better analog properties than their conventional inversion mode counterparts. The ITRS prediction of increase in operation speed and improved drive current for devices with strained Si in n-type and p-type junctionless trasnsistor and strained channels are supported in the paper [22]. High temperature performance [23,24] and short channel effects [25,26] of such a structures have also been investigated. Dr. A Kranti in [27] has shown the huge potential of Junctionless MOSFETs for Ultra Low Power analog/RF applications. He has also concluded that such a structure requires simpler fabrication process as there is no need for any source-drain region formation and related engineering. For channel length of as small as 16nm Ge bulk nanowire junctionless transistor is shown to have a subtheshold slope of 77mV/decade and drain-induced-barrier-lowering of 70mV for an on-off current ratio of  $1.1 \times 105$  as has been shown in [28]. Papers [29,30] establish the simplicity of fabrication steps of Junctionless

Transistors as opposed to that of the conventional CMOS process flow. Junctionless Transistor based inverter has also been proposed which shows high on off current ratio and better short channel behaviour in 10nm technology node and even beyond. Research is also being pursued to fabricate Junctionless Transistor based Nanoscale Appplication Specific Integrated Circuits [31]. Many literatures [32-34] on the drain current models and compact models of the junctionless transistors are also being reported.

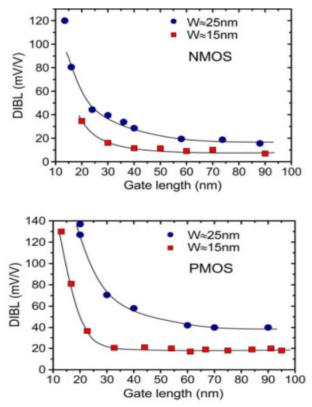

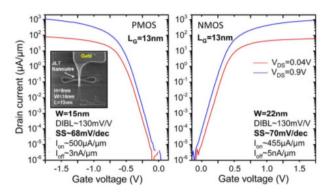

Figure 4a and b:Measurements of DIBL [36] as a function of gate length for both NMOS and PMOS trigate JL NW MOSFETs.

Figure 5:I<sub>D</sub>-V<sub>GS</sub> Charecteristics[36]

Figure 4a and b shows measurement of DIB1 and Figure 5 shows  $I_D$ - $V_{GS}$  Charecteristics as given in [36] for trigate

junctionless nanowire transistor which shows better performance at 13nm node point for high K/metal gate stack.

### 4. CONCLUSION AND DISCUSSION

Many research groups have considered Junctionless Transistor(JLT) as a potential research domain and their contributions have provided enough evidence to consider JLT as a future logic device.

Better high temperature performance, improved shorth channel behavior and simple fabrication step makes it an automatic choice.

#### 5. FUTURE SCOPE

With latest research establishing the superiority of the JLT over contemporary alternatives, the compact modelling of JLT is the most important future scope. SPICE based compact model development for such a structure can help in the circuit implementation and realise the Moore's Law for future semiconductor industry.

Use of non-silicon semiconducting materials in such a structures may result in improved performance metrices. High-K gate stack has already been investigated but GaAs channel JLT needs to be studied to find out if it shows better high frequency responses and low power performance of non-silicon devices may also be further looked into.

#### 6. ACKNOWLEDGEMENT

The authors acknowledge Department of Science & Technology, Government of India, for the support under the FIST programme of the Department of Computer Science and Engineering, West Bengal University of Technology. Mr. Subhradip Das acknowledges the support of TEQIP Phase-II for funding his Research Assistantship

#### REFERENCES

- [1] Dan Rosso."Semiconductor Industry Posts Record Sales in2013."Internet:https://www.semiconductors.org/news/2014/03 /global sales reports 2013 semiconductor industry posts record sales in 2013 3rd February 2014, [10 th February,2014]

- [2] Moore, Gordon E. (1965). "Cramming more components onto integrated circuits" (PDF). Electronics Magazine. p. 4. Retrieved 2006-11-11.

- [3] Taur, Yuan "Invited talk: CMOS device scaling Past, present, and future" Microelectronics And Electron Devices (WMED), 2014 IEEE Workshop On, 18-18 April 2014.

- [4] A. Toriumi, M. Iwase, and M. Yoshimi, "On the performance limit for Si MOSFET: Experimental study," IEEE Trans. Electron Devices, vol. 35, pp. 999–1003, 1988

- [5] Farzin Assad, Zhibin Ren, Dragica Vasileska, Member, Supriyo Datta, Mark Lundstrom, "On the Performance Limits for Si MOSFET's:

Theoretical Study", IEEE Transactions On Electron Devices, Vol. 47, No. 1, January 2000.

- [6] ITRS Update 2012, Available Online: www.itrs.net/Links/2012ITRS/Home2012.htm[10th February,2014]

- [7] Morten, B.; Canali, C.; Ferla, G.; Taroni, A."Strain Sensitivity of MOSFET Devices" Instrumentation and Measurement, IEEE Transactions on (Volume:26, Issue: 4), Dec. 1977.

- [8] Lam, H.W, Sobczak, Z.B, Pinizzotto, R.F, Tasch, A.F, "MOSFETs Fabricated in {100} single crystal silicon-on-oxide obtained by a laser-induced lateral seeding technique" Electron Devices Meeting, 1980 International (Volume:26),1980.

- [9] Xuejue Huang, Wen-Chin Lee, Charles Kuo, Hisamoto, D, Leland Chang, Kedzierski, J, Anderson, E, Takeuchi, H. ; Yang-Kyu Choi ; Asano, K, Subramanian, V, Tsu-Jae King, Bokor, J, Chenming Hu, "Sub 50-nm FinFET: PMOS", Electron Devices Meeting, 1999. IEDM '99. Technical Digest. International,pp.67 – 70,5-8 Dec. 1999.

- [10] Hisamoto, D, Wen-Chin Lee, Kedzierski, J, Takeuchi, H, Asano, K, Kuo, C, Anderson, Erik, Tsu-Jae King, Bokor, J, Chenming Hu, "FinFET-a self-aligned double-gate MOSFET scalable to 20 nm" Electron Devices, IEEE Transactions on (Volume:47, Issue: 12), pp.2320 – 232, Dec 2000.

- [11] Chenming Hu , "SOI and nanoscale MOSFETs" Device Research Conference, pp.3 – 4, 2001, 25-27 June 2001.

- [12] Xuejue Huang, Wen-Chin Lee, Kuo, C, Hisamoto, D, Chang, L, Kedzierski, J, Anderson, Erik, Takeuchi, H, Choi, Yang-Kyu; Asano, K.; Subramanian, Vivek, Tsu-Jae King, Bokor, J, Chenming Hu"Sub-50 nm P-channel FinFET", Electron Devices, IEEE Transactions on (Volume:48, Issue: 5), pp. 880 – 886, May 2001.

- [13] Tang, S.H, Chang, L, Lindert, N, Yang-Kyu Choi, Wen-Chin Lee, Xuejue Huang, Subramanian, V., Bokor, J, Tsu-Jae King, Chenming Hu, "FinFET-a quasi-planar double-gate MOSFET", Solid-State Circuits Conference, 2001. Digest of Technical Papers. ISSCC. 2001 IEEE International, pp. 118 – 119, 7 Feb. 2001.

- [14] Mattausch, H.J, Chan, M, He, J, Koike, H, Miura-Mattausch, M, Nakagawa, T, Park, Y.J, Tsutsumi, T, Yu, Z, "Development of multi-gate mosfet models for circuit simulation with a compact modeling platform", IET Conference Publication, 15th International Conference on Mixed Design of Integrated Circuits and Systems, 2008. MIXDES 2008, pp. 59- 64 2008.

- [15] Knoblinger, G, Pacha, C, Kuttner, F, Marshall, A., Russ, C., Haibach, P, Patruno, P, Schulz, T., Arnim, K.V, Engelstaedter, J.P, Bertolissi, L, Xiong, W, Cleavelin, C.R, Schruefer, K, "Multi-Gate MOSFET Design", IEEE Conference Publications, Proceeding of the 36th European Solid-State Device Research Conference, 2006. ESSDERC 2006.,pp. 65- 68, 2006.

- [16] Physics of Semiconductor Devices By Simon M. Sze, John Wiley &Sons,2nd edition,pp.469-485.

- [17] J.P.Colinge,et.al, "Nanowire transistors without junctions" Nature nanotechnology, Vol.5, [Online] https://www.nature.com/naturenanotechnology, March, 2010.

- [18] Jean-Pierre Colinge, Junctionless metal-oxide-semiconductor transistor. US Patent, US 8178862 B2,May 15( 2012)

- [19] A. Kranti, R. Yan, C.-W. Lee, I. Ferain, R. Yu, N. Dehdashti Akhavan, P. Razavi, JP Colinge, "Junctionless Nanowire Transistor (JNT): Properties and Design

Guidelines", Proceedings of the European Solid- State Device Research Conference (ESSDERC), 2010, pp.357-360.

- [20] R.T. Doria 1, M.A. Pavanello, R.D. Trevisoli1, M. de Souza, C.W. Lee3, I. Ferain, N. Dehdashti Akhavan, R. Yan, P. Razavi, R. Yu, A. Kranti and J.P. Colinge"Analog Operation of Junctionless Transistors at Cryogenic Temperatures", IEEE International SOI Conference (SOI), 2010, pp.1-2.

- [21] Rodrigo Trevisoli Doria, Marcelo Antonio Pavanello, Renan Doria Trevisoli, Michelly de Souza, Chi- Woo Lee, Isabelle Ferain, Nima Dehdashti Akhavan, Ran Yan, Pedram Razavi, Ran Yu, Abhinav Kranti, and Jean-Pierre Colinge, "Junctionless Multiple-Gate Transistors for Analog Applications", IEEE Transactions on Electron Devices, (Volume:58, Issue: 8),pp. 2511-2519, Aug.2011.

- [22] Jean-Pierre Raskin, Jean-Pierre Colinge, Isabelle Ferain, Abhinav Kranti, Chi-Woo Lee, Nima Dehdashti Akhavan, Ran Yan, Pedram Razavi and Ran Yu2, "Mobility Improvement In Nanowire Junctionless Transistors By Uniaxial Strain", IEEE International SOI Conference (SOI), 2010,pp.1-2.

- [23] Chi-Woo Lee, Adrien Borne, Isabelle Ferain, Aryan Afzalian, Member, IEEE, Ran Yan, Nima Dehdashti Akhavan, Pedram Razavi, and Jean-Pierre Colinge, "High-Temperature Performance of Silicon Junctionless MOSFETs", IEEE Transactions on Electron Devices, (Volume:57, Issue: 3),pp.-620-625,March 2010.

- [24] Michelly de Souza, Marcelo A. Pavanello, Renan D. Trevisoli, Rodrigo T. Doria, and Jean-Pierre Colinge, "Cryogenic Operation of Junctionless Nanowire Transistors", IEEE Electron Device Letters, (Volume:32, Issue: 10), pp.1322-1324, Oct. 201.

- [25] P. Razavi, G. Fagas, I. Ferain, N. Dehdashti Akhavan, R. Yu, J.P. Colinge, "Performance Investigation of Short-channel Junctionless Multigate Transistors",12th International Conference on Ultimate Integration on Silicon (ULIS), 14-16 March 2011, pp.1-3.

- [26] C.W. Lee, I. Ferain, A. Kranti, N. Dehdashti Akhavan, P. Razavi, R. Yan, R. Yu, B. ONeill, A.Blake, M. White, A.M. Kelleher, B. McCarthy, S. Gheorghe, R. Murphy, J.P. Colinge, "Short-Channel Junctionless Nanowire Transistors", International Conference on Solid State Devices and Materials,28-30 Sept. 2011.

- [27] Dipankar Ghosh, Mukta Singh Parihar, G. Alastair Armstrong, and Abhinav Kranti, "High Performance Junctionless MOSFETs for Ultralow-Power Analog/RF Applications", IEEE Electron Device Letters, (Volume:33, Issue: 10), pp.1477-1479, Oct. 2012.

- [28] Ran Yu, Samaresh Das, Isabelle Ferain, Pedram Razavi, Maryam Shayesteh, Abhinav Kranti, Ray Duffy, and Jean-Pierre Colinge, "Device Design and Estimated Performance for p-Type Junctionless Transistors on Bulk Germanium Substrates", IEEE Transactions on Electron Devices, (Volume:59, Issue: 9), pp.2308-2313, Sept.2012.

- [29] J.P. Colinge, C.W. Lee, A. Afzalian, N. Dehdashti, R. Yan, I. Ferain, P. Razavi, B. ONeill, A. Blake, M. White, A.M. Kelleher, B. McCarthy and R. Murphy, "SOI Gated Resistor: CMOS without Junctions," IEEE International SOI Conference, 5-8 Oct. 2009, pp.1-2.

- [30] Chan-Hoon Park, Myung-Dong Ko, Ki-Hyun Kim, Chang-Woo Sohn, Chang Ki Baek, Yoon-Ha Jeong Jeong-Soo Lee, "Comparative Study of Fabricated Junctionless and Inversion-

mode Nanowire FETs", 69th Annual Device Research Conference (DRC), 20-22 June 2011, pp.179-180.

- [31] Pritish Narayanan, Pavan Panchapakeshan, Jorge Kina, Chi On Chui and Csaba Andras Moritz, "Integrated Nanosystems with Junctionless Crossed Nanowire Transistors," 11th IEEE Conference on Nanotechnology (IEEE-NANO), 15-18 Aug. 2011, pp.845-848.

- [32] Juan Pablo Duarte, Sung-Jin Choi, and Yang-Kyu Choi, "A Full-Range Drain Current Model for Double-Gate Junctionless Transistors," IEEE Transactions on Electron Devices, (Volume:58, Issue: 12), pp.4219 - 4225, Dec. 2011.

- [33] Trevisoli, R.D. Doria, de Souza, Pavanello, "Drain Current Model for Junctionless Nanowire Transistors," 8th International Caribbean Conference on Devices, Circuits and Systems (ICCDCS), 14-17, March 2012, pp.1-4.

- [34] Renan Doria Trevisoli, Rodrigo Trevisoli Doria, Michelly de Souza, Samaresh Das, Isabelle Ferain, and Marcelo Antonio Pavanello, "Surface-Potential-Based Drain Current Analytical Model for Triple-Gate Junctionless Nanowire Transistors" IEEE Transactions on Electron Devices, (Volume:59, Issue: 12), pp.3510 - 3518, Dec. 2012.

- [35] Carlos Galup-Montoro, Marcio Cherem Schneider, "Mosfet Modelling for Circuit Analysis and Design", World Scientific, International Series on Advances in Solid State Electronics and Technology(ASSET), pp.2-3.

- [36] S. Barraud, M. Berthomé, R. Coquand, M. Cassé, T. Ernst, M.-P. Samson, P. Perreau, K. K. Bourdelle, O. Faynot, and T. Poiroux, "Scaling of Trigate Junctionless Nanowire MOSFET With Gate Length Down to 13 nm", IEEE Electron Device Letters, Vol. 33, No. 9, September 2012.